-

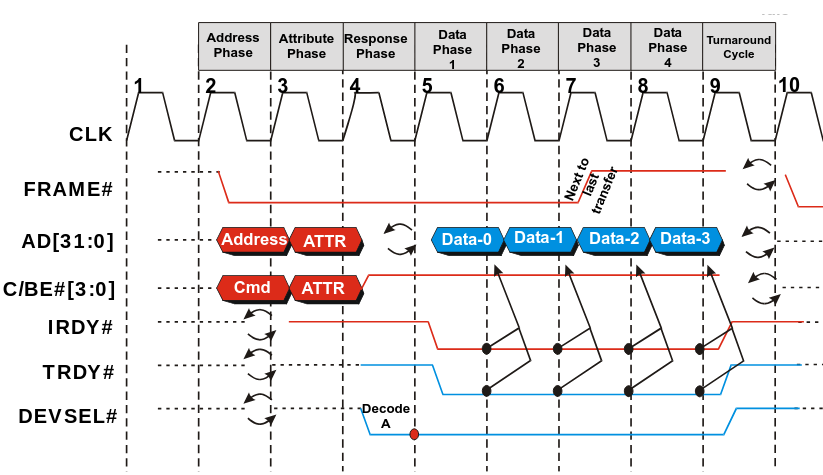

No Wait States After First Data Phase

- In PCI, a target could insert wait states during any data phase if it wasn’t ready.

- In PCI-X, wait states are only possible before the first data phase.

- After the first data is transferred, the rest must flow continuously (no more stalls).

✅ Why? Because PCI-X gives the target device all the info up front (see next point).

- Attribute Phase = Transfer Size Known in Advance

- PCI-X adds an Attribute phase to the transaction.

- This phase tells the target device how much data will be transferred.

- The target can pre-allocate buffer space and prepare, avoiding mid-transaction delays.

- Burst-Oriented Transfers

- Most PCI-X cycles are burst transactions (not single data beats).

- Transfers are typically done in 128-byte blocks (32 dwords if bus is 32-bit wide, or 16 dwords if 64-bit wide).

- Bursts reduce bus overhead and maximize throughput.

- Efficiency Gains

- Since wait states are minimized and data is moved in large, predictable bursts,

→ The bus has higher utilization.

→ Devices can manage buffers more efficiently. - This is one of the main reasons PCI-X outperforms legacy PCI despite similar signaling.

- Since wait states are minimized and data is moved in large, predictable bursts,